SiFive presents RISC-V product overview

SiFive presents RISC-V product overview

By Pradeep Chakraborty

Pradeep Chakraborty

SiFive recently presented the RISC-V product overview. Krste Asanovic, co-founder and chief architect, said: “Have you ever heard of a $1 billion hardware company with 13 employees? Instagram turned into a $1 billion acquisition with only 13 employees.

“SiFive provides RISC-V core IP. SiFive RISC-V core IP product offering includes E Cores and U Cores. E Cores are the industry leading 32- and 64-bit embedded cores. U Cores are the high performance 64-bit application cores.”

The Core Series offer unique design points which can be customized for application-specific requirements. Standard Cores are pre-configured implementations of Core Series, free RTL and FPGA evaluations.

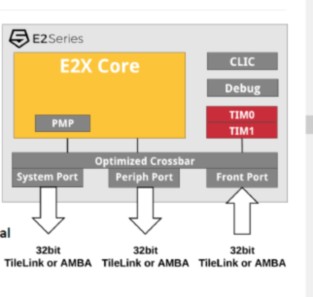

E2 Series RISC-V Core IP

E2 Series is the smallest, most efficient RISC-V MCU family. It is:

– RV32IMAFC capable core

– 2-3 stage, optional, Harvard Pipeline

It is configurable to meet application specific needs. It is the first RISC-V core with support for for the RISC-V Core local interrupt controller (CLIC). Drop In Cortex-M0+ and Cortex-M3/M4 replacement.

E21 is 12 percent higher performance per MHz vs Cortex-M4 in CoreMark, when using equivalent GCC Compilers. E20 is 28 percent higher performance per MHz vs Cortex-M0+ in CoreMark, when using equivalent GCC Compilers.

SiFiveE3 and E5 Series RISC-V Core IP are high performance 32-bit and 64-bit RISC-V MCUs. Features include pipelined multiapplication unit, multicore support, fast interrupts and memory protection.

U5 Series RISC-V Core IP

SiFive U5 Series RISC-V Core IP is 64-bit RISC-V Multicore Linux-capable. The U5-MC allows for instantiation of up to 9 U5 and/or E5 cores as well a configurable Level 2 cache. Flexible memory system allows for application-specific resource partitioning.

It has broad market applications – general-purpose embedded, industrial, IoT, high-performance real -time embedded, automotive.

The U54 -MC4 Standard Core is also 64-bit RISC-V multicore Linux capable.

“RISC -V delivers a platform for innovation, unshackled from the proprietary interface of the past. This freedom allows us to bring compute closer to data to optimize special-purpose compute capabilities targeted at Big Data and Fast Data applications,” according to Martin Fink, CTO, Western Digital.